Das sind jetzt Einblicke und Detail-Fotos

von DLT Geräten samt unserem Kommentar aus Sicht der Ingenieure, damit auch der Laie einen kleinen Eindruck bekommt, wovon wir überhaupt reden und wie es in so einem DLT-Laufwerk aussieht:

Einblick in die DLT-8000 Chips

Das DLT-8000er Laufwerk war vorerst das Ende der DLT Baureihe. Nach unserer Meinung wurde dort das Letzte an machbarer Technologie aus dem System und dem DLT Type IV Band herausgekitzelt, das überhaupt mit dieser Technik machbar war.

Auf dem DLT-8000 Board sind 4 große Chips, 4 mittlere Chips und eine ganze Menge an Speicherbausteinen und Pufferbausteinen aufgelötet.

Die Platine scheint ein sogenannter beidseitiger vierfach Multilayer zu sein, denn man erkennt die inneren Leiterbahn-Schichten nicht.

Wir wollen hier ein bißchen mehr für den interessierten Techniker darstellen, soweit wir das alles enträtseln konnten.

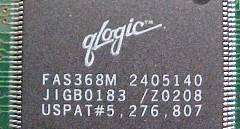

Ein Ärgernis bei allen DLTs ist die miserable netto Performance von nur 10 MB/s an der SCSI Schnittstelle. Dafür ist der Qlogic Chip verantwortlich.

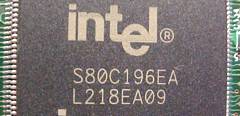

Intel S80C195

Die Intel S8xC195 Industrieprozessor Familie soll insbesondere schnelle I/O Operationen durchführen können. Dieser 16Bit Prozessor soll also "bestimmte tolle Eigenschaften" im schnellen Echtzeitbetrieb haben. Für den Betrieb der Seriellen Schnittstelle zum Roboter-Controller der Library ist er mit Sicherheit völlig überdimensioniert, außer man brauchte damals bereits den 16 Bit Bus zum Transfer der Daten zu den anderen CPUs.

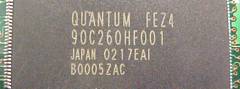

Quantum 90C260

Dieser ASIC (Kunden spezifischer Prozessor) scheint zwei Frequenzgeneratoren samt Rückkoppelung des Regelkreises vom Tachogenerator zu enthalten.

Damit werden die beiden Antriebs-Motoren mit absolut fließender Frequenz so versorgt, daß der DLT Tachogenerator eine absolut gleichbleibende Geschwindigkeit zurück meldet.

Datenblätter oder Beschreibungen haben wir nicht gefunden.

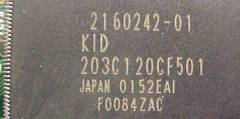

2160242

Einer von den beiden ganz großen Chips, die auch sehr heiß werden. Die Datenblätter dieses Chips suchen wir auch noch.

Qlogic FAS368M Fast Architecture SCSI Processor

Dieser Chip ist das SCSI Interface zum Server oder auch Host genannt. In diesem Chip steckt auch die unglückliche Begrenzung auf 10 MB/s maximale netto Datentransferrrate. Die anderen Chips könnten eigentlich mehr.

Feature Summary

- Compliance with ANSI X3T10/1142D SCSI Parallel Interconnect-2 (SPI-2) standard

- Compliance with ANSI SCSI configured automatically (SCAM) protocol levels 1 and 2

- Sustained SCSI data transfer rates of up to:

40 Mbytes/sec synchronous (Ultra and wide SCSI) - und hier steckt der "Kasus Knacktus" in dieser lapidaren Aussage,

die man gerne überliest :

14 Mbytes/sec asynchronous (wide SCSI)

und das sind eben nur etwas über 10 MB/s netto netto !!!! - Synchronous DMA timing; DMA speed of 50 Mbytes/sec

- REQ and ACK programmable assertion and deassertion control

- Support for hot plugging

- Target and initiator block transfer sequences

- Bus idle timer

- Split-bus architecture

- Pipelined command structure

- On-chip, single-ended SCSI transceivers (48-mA drivers)

- On-chip, multimode, low voltage differential (LVD) drivers

- On-chip differential sense decoder

- Initiator and target roles

- Active negation

- 16-bit recommand counter

- Differential mode

- SCSI bus reset watchdog timer

Hier kommen die Hersteller Werbesprüche aus 1996 oder noch früher :

- The FAS368M is a new addition to the QLogic fast architecture SCSI processor (FAS) chip family. The FAS368M supports internal multimode LVD and single-ended (SE) transceivers, which allow the chip to support LVD and SE operations in initiator and target roles.

- The FAS368M is a single-chip controller for use in host and peripheral applications. To ensure firmware compatibility and provide FAS366U customers a seamless upgrade path, the FAS368M uses the same SCSI core, foundry, and process as the FAS366U. Note that the FAS368M package size, pin out, and transceivers differ from the FAS366U.

- The FAS368M implements QLogic’s new SCSI target and initiator block transfer sequences. The block sequences reduce firmware overhead and are composed of the following new commands: Target Block Sequence (including the bus idle timer), Initiator Block Sequence, Load/Unload Block Registers sequences, Abort Block Sequence, and Disconnect Abort Block Sequence. The FAS368M supports both single-ended and differential mode SCSI operations and operates in initiator and target roles.

- The FAS368M has been optimized for interaction with a DMA controller and the controlling microprocessor. The versatile split-bus architecture supports various microprocessor and DMA bus configurations. A separate 8-bit microprocessor bus (PAD) provides access to all internal registers, and a 16-bit DMA bus (DB) provides a path for DMA transfers through the FIFO. Each bus is protected by a parity bit (byte-wide parity) to improve data integrity. During data transfer, the microprocessor has instant access to status and has the ability to execute commands.

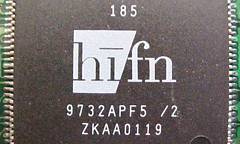

Hi/Fn Kompressionschip 9732APF5

Dieser Chip verarbeitet die Datenkompression in beide Richtungen. Der Chip-Hersteller Hi/Fn beschreibt die Performance immer am mittleren Kompressionsgrad von 2:1. Daher kommt sicher auch die werbewirksame Bezeichnung der DLT´s als 40/80 für den DLT-8000.

In diesem Chip ist immer noch der STAC Defacto Standard der verlustfreien Datenkompression. So sieht es der Hersteller: Chip Typ 9732 - Fast processor used for high-speed tape drives, printers and other applications.

Wichtig zu wissen, mehr als Komprimieren kann der Chip und auch der STAC Algorithmus auch nicht und ZIP´s, PDF´s, MP3`s und JPEG`s und GIF´s kann er auch nicht weiter runter komprimieren. Diese Datei-Formate sind so weit "ausgeknautscht", da werden die weiteren Versuche, also die Ergebnisse, wieder größer.

Mehr darüber steht ganz unten auf dieser Seite.

TC14L020AF

Der Chip TC14L020 ist ein 2K usable gate CMOS gate array.

Motorola CPU MC68EC020

Das ist die abgeschminkte 25 MHz Version (ähnlich Duron und Sempron) des legendären 68020 Prozessors von Motorola. Dieser hier geht nur mit 16 Bit breiten Verbindungen nach draußen, werkelt aber innen drinnen mit vollen 32 Bit. Das ist eine sehr leistungsfähige CPU, die man von den ersten richtigen Apples oder MACs her kennt.

Wir nehmen an, diese 25 MHz CPU koordiniert den DMA Betrieb der anderen Prozessoren.

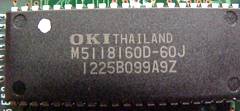

OKI M5116160D

Compressing data - Datenkompression im DLT Laufwerk

In Hifn's LZS compression, the repetitive characters must be within about 2,000 characters (2,048 bytes) of each other. It is true, that, if Hifn used a larger chunk of text, it would achieve more compression, but it would also slow down the process.

The strength of LZS is, that it produces an optimum combination of compression and performance. LZS achieves "lossless compression" which simply means, no data is lost during compression and decompression. Lossless compression reduces data typically by about 1/2 - but nothing is ever lost. With LZS, customers achieve acceleration without deterioration.

Was will uns das im Klartext sagen ?

Also:

Die Experten sprechen von einer mittleren 2:1 Kompression und dabei immer und absolut verlustlos. Das ist also der Knackpunkt im Vergleichzu MP3, MPEG2 oder MPEG4 oder JPEG. Sie verarbeiten dabei immer nur 2 Megabyte Daten-Blöcke, damit die Kompression / Dekompression nahezu in Echtzeit abläuft. Eigentlich könnten Sie ja mehr am Stück komprimieren wie es z.B. das ZIP Programm im PC bewerkstelligt, jedoch dann nicht im Streaming Modus.

Bei den HP DAT Loadern kann man es auch deutlich im Display sehen, die zeigen das nämlich während des Schreibens an, die Kompression schwankt immer so zwischen 1,2 und 1,9. Durch diese 2 MB Kompressions-Blockgröße ist die gesamte Kompressionsrate also deutlich limitiert. Einen Faktor von 10:1, 20:1 oder mehr wie bei ZIP Dateien kann es so gar nicht geben, auch nicht bei riesigen Datenbankdateien (MSSQL) mit "nichts" drinnen.

Wenn Sie können, komprimieren Sie vorher auf dem Server so viel wie Sie können und schalten Sie die DLT Hardware Kompression ab.